-

728x90

I2C(Inter Intergraed Circuit)은 아래 회로와 같이 SDA(데이터)와 SCL(클럭)의 두 가닥의 선으로 프로세서 간에 통신을 할 수 있도록 하는 규약입니다. 이름에서 'I'가 2번 사용되어서 I2C 또는 IIC 라고도 불리고, 선 두 가닥으로 통신하는 점 때문에 Two-wire Interface(TWI) 라고도 불립니다. 저는 하드웨어 엔지니어는 아니라서 프로그래머 입장에서 알아야 하는 지식에 초점을 맞추어 설명 하겠습니다.

[그림1] I2C 인터페이스 I2C 칩은 송신기(Master)와 수신기(Slave)로 구분되어 집니다. 또, 이론상으로는 I2C는 SPI와 달리 한 버스에 여러 개의 마스터와 슬레이브 장치가 연결될 수 있습니다.

[그림 2] I2C 블록 다이어그램 그런데, 마스터가 여러 개면 한 마스터가 통신 선을 선점했을 때를 고려해야 하기 때문에 시스템이 복잡해지고, 슬레이브도 주소만 겹치지 않는다면 되도록 많이 연결 할 수 있지만 한 버스에 슬레이브를 많이 달면 원인을 찾기 힘든 이상 동작도 발생하기도 합니다. 그래서 보통 한 버스에 마스터는 한 개, 슬레이브를 2~3개 정도 사용하도록 설계해주십사 하드웨어 엔지니어에게 요청합니다.

하지만 구지 요청하지 않아도 저는 하드웨어 엔지니어분께서도 저렇게 마스터를 여러 개 연결하여 구성하시는 것은 아직까지 보지 못했습니다. 또 요즘 대부분의 프로세서는 I2C 전용 컨트롤러 채널을 2개 이상 가지고 있고, 속도가 중요하지 않다면 남는 핀(GPIO)으로 구현이 가능하기 때문에 구태여 위험을 안고 설계를 하지는 않으십니다.

그럼 I2C 패킷을 살펴보겠습니다.

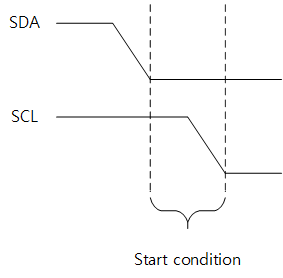

[그림 3] I2C 패킷 I2C는 UART와 비슷하게 Start bit로 시작합니다. 통신이 쉬고 있을 경우 SDA와 SCL은 모두 High 상태를 유지합니다(그래서 [그림 2]에서 각각의 라인을 VCC와 연결하고 있습니다). 그러다가 마스터에서 통신을 시작하기 위해 SDA를 먼저 Low로 떨어뜨립니다. 그 후에 SCL도 Low로 떨어뜨립니다. 그러면 슬레이브 장치들은 SDA와 SCL이 Low로 떨어진 것을 감지하여 통신 시작 조건(Start condition)이 성립됩니다. 떨어질 때 감지하는 것이 아니고 떨어진 것을 감지함으로 Falling Edge라고 합니다.

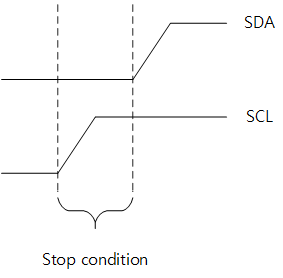

[그림4] Start condition Stop 조건은 위와 반대로 SCL이 먼저 그 후에 SDA가 High로 올라옵니다.

[그림5] Stop condition Start condition을 보낸 후 슬레이브 주소를 보내는데 클럭 타이밍에 맞춰(동기화하여) 데이터를 보내줍니다. 마스터가 SCL을 High로 올렸다가 Low로 내리면 1클럭인데, 1클럭에 1비트를 전송합니다.

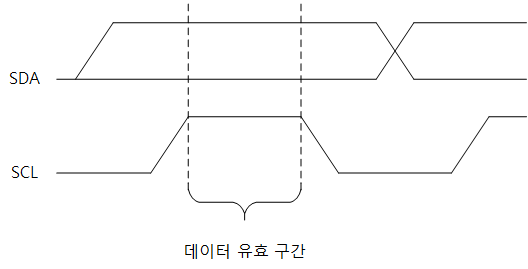

SCL을 High로 올려 클럭을 보내기 전에 보내야 할 데이터 비트가 1이면 SDA를 High로 올리고, 0이면 Low로 내립니다. 그 후에 SCL이 High로 올라가는데 이 때 슬레이브는 SCL이 다시 Low로 떨어지기 전까지 SDA 상태를 읽어갑니다.

[그림6] 데이터 유효 구간 슬레이브 주소는 7비트 입니다(10비트 주소도 있지만 그건 아래에서 설명하겠습니다). 위와 같은 방식으로 7비트를 전송하고 나면 데이터 방향 비트를 보내는데, 방향 비트란 데이터를 읽어올 것인지 쓸 것인지를 알려줍니다. 읽어온다면 1, 쓴다면 0을 전송합니다.

※ 참고: 데이터시트에는 Slave address가 A0h(10100000b) 인데, 드라이버 소스 코드를 보면 0x50(01010000b)이라고 해놓은 것들을 볼 수 있습니다. 이는 주소 7비트와 방향 비트를 합쳐서 8비트로 표현했을 때와 주소 7비트로만 표현 했을 때의 차이입니다. 어쩔 때는 반대로 데이터시트는 7비트, 소스 코드는 8비트로 표현되어 있을 때도 있으니 주의하셔야 합니다.

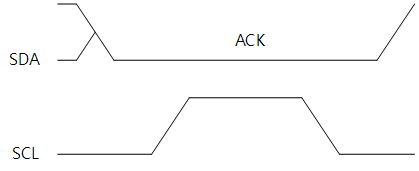

슬레이브들 중 자신의 주소가 호출된 슬레이브는 ACK를 보내 마스터에게 응답을 해줍니다. 위에서도 언급했지만 SDA와 SCL은 VCC에 연결되어 있어 통신이 쉴 때는 High를 유지하려는 특성이 있는데, 마스터는 주소 7비트를 전송하고 난 후 SDA를 High가 되도록 풀어줍니다. 이 때 주소를 호출 받은 슬레이브는 SDA를 Low로 잡아 떨어뜨리며 응답합니다. 만약 주소를 전송했는데 SDA가 Low가 아니라 High라면(NAK) 주소가 잘못되었거나 슬레이브 칩이 동작을 하지 않을 가능성이 있습니다. 그럴때는 소스 코드를 다시 한 번 확인하시고, H/W 엔지니어와 함께 디버깅을 해보십시오.

[그림7] ACK ACK가 확인되면 방향 비트에 따라 다음 데이터는 마스터가 보내주던가 슬레이브에서 보내주는 데이터를 읽습니다. 그렇게 데이터 8비트를 통신하고 나면 슬레이브가 ACK를 보내줍니다. 그러나 데이터를 1바이트만 아니라 여러 바이트 송수신 할 수 있는 칩이라면 ACK는 마지막 바이트에서만 보내줄 수도 있습니다. 여러 바이트를 송수신할 때는 꼭 데이터시트를 확인해보시기 바랍니다.

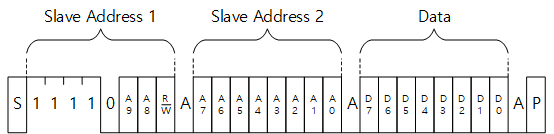

위에서 10비트 주소도 있다고 알려드렸는데, 10비트 주소를 보낼 때는 다음과 같이 주소를 2번에 나눠서 보내게 됩니다. 대신 7비트 주소와 차별을 두기 위해서 주소가 11110xx로 시작합니다. 그래서 첫 번째 바이트의 하위 2비트와 두 번째 바이트의 8비트와 결합하여 10비트 주소를 이룹니다. 7비트 장치들은 11110xx로 시작하는 주소는 무시하기 때문에 7비트 주소 칩과 10비트 주소 칩은 한 버스에서 함께 사용할 수도 있습니다.

[그림 8] 10비트 주소 패킷 참고 사이트 및 서적

728x90'하드웨어' 카테고리의 다른 글

IR 신호 구성 (NEC 방식) (0) 2013.03.13